# **Managing the Memory Hierarchy in GPUs**

Saumay Dublish

Doctor of Philosophy

Institute of Computing Systems Architecture

School of Informatics

University of Edinburgh

2018

### **Abstract**

Pervasive use of GPUs across multiple disciplines is a result of continuous adaptation of the GPU architectures to address the needs of upcoming application domains. One such vital improvement is the introduction of the on-chip cache hierarchy, used primarily to filter the high bandwidth demand to the off-chip memory. However, in contrast to traditional CPUs, the cache hierarchy in GPUs is presented with significantly different challenges such as cache thrashing and bandwidth bottlenecks, arising due to small caches and high levels of memory traffic. These challenges lead to severe congestion across the memory hierarchy, resulting in high memory access latencies. In memory-intensive applications, such high memory access latencies often get exposed and can no longer be hidden through multithreading, and therefore adversely impact system performance.

In this thesis, we address the inefficiencies across the memory hierarchy in GPUs that lead to such high levels of congestion. We identify three major factors contributing to poor memory system performance: first, disproportionate and insufficient bandwidth resources in the cache hierarchy; second, poor cache management policies; and third, high levels of multithreading. In order to revitalize the memory hierarchy by addressing the above limitations, we propose a three-pronged approach. First, we characterize the bandwidth bottlenecks present across the memory hierarchy in GPUs and identify the architectural parameters that are most critical in alleviating congestion. Subsequently, we explore the architectural design space to mitigate the bandwidth bottlenecks in a cost-effective manner. Second, we identify significant inter-core reuse in GPUs, presenting an opportunity to reuse data among the L1s. We exploit this reuse by connecting the L1 caches with a lightweight ring network to facilitate inter-core communication of shared data. We show that this technique reduces traffic to the L2 cache, freeing up the bandwidth for other accesses. Third, we present *Poise*, a machine learning approach to mitigate cache thrashing and bandwidth bottlenecks by altering the levels of multithreading. *Poise* comprises a supervised learning model that is trained offline on a set of profiled kernels to make good warp scheduling decisions. Subsequently, a hardware inference engine is used to predict good warp scheduling decisions at runtime using the model learned during training. In summary, we address the problem of bandwidth bottlenecks across the memory hierarchy in GPUs by exploring how to best scale, supplement and utilize the existing bandwidth resources. These techniques provide an effective and comprehensive methodology to mitigate the bandwidth bottlenecks in the GPU memory hierarchy.

## **Lay Summary**

Our day-to-day life revolves around the marvels of computational progress. Ranging from small-scale devices such as smart phones and fitness trackers to large-scale services such as search engines and cloud computing — all are rooted in the tremendous progress made by the computer industry. Over the last decade, a lot of this progress is credited to the success of *Graphics Processing Units* or GPUs. Recent advancements have led to significant improvements in the graphics performance, which is evidenced by high resolution games and realistic animation films. In addition, modern GPUs have also greatly influenced general-purpose areas such as artificial intelligence and healthcare.

Modern GPUs pose several challenges to computer architects. These challenges can be explained through a *restaurant* analogy. In older times, restaurant kitchens lacked modern storage equipments to preserve perishable products. Therefore, chefs had to repeatedly visit the distant grocery stores to buy raw materials for their recipes. With the advent of in-house storage facilities such as refrigerators, number of trips to the grocery stores could be reduced by storing or *caching* perishable groceries more proximately. A problem arises when large number of chefs pose conflicting storage needs. In such a scenario, shared storage proves to be insufficient in terms of capacity as well as the available parallelism in accessing the shared storage. This results in large queues and congestion at the refrigerators (and even at the grocery stores). For a given amount of storage and floorspace, the congestion problem can be addressed primarily in three ways. Firstly, by allowing multiple chefs to access the storage at the same time; for instance, by adding independent doors to each shelf in the refrigerator. Secondly, by encouraging chefs to cooperatively share common products to avoid redundant trips to the refrigerator by multiple chefs for the same items. Thirdly, by limiting the number of chefs so that their storage demand matches the available kitchen resources, while also ensuring constant food supply to the customers. Similar to the restaurant scenario, where multiple chefs process raw food by following a recipe, GPUs have multiple processors that crunch raw data by following a set of instructions. GPUs retrieve this data from storage elements such as proximate caches and distant memories, and then pour it into the computational machinery inside the GPU to complete a task. Similar to food stores, shared memory resources in GPUs also suffer from severe congestion. In this thesis, we address the high levels of congestion in GPUs and propose three solutions, analogous to the solutions proposed for the restaurant problem. In effect, we investigate ways to efficiently manage the shared memory resources in GPUs.

## **Acknowledgements**

I would like to express my deep gratitude to my advisor, Prof. Nigel Topham, for his guidance, advice and kindness throughout my graduate studies. Nigel gave me the freedom and encouragement to explore new problems, which was vital in enabling me to mature as a researcher. He always had the time and utmost patience whenever I needed advice and direction in my research. I am extremely grateful for his mentorship.

I would like to thank my co-advisor, Dr. Vijay Nagarajan, for his invaluable counsel. His confidence in my abilities and constant encouragement during the highs and lows of my graduate studies kept me motivated, and inspired me to pursue meaningful research. The door to his office was always open for discussions and brainstorming, which proved extremely useful in shaping my work. I am very grateful to him for all the guidance and support.

I would like to thank Dr. Boris Grot for being part of the annual review committee and providing valuable advice and suggestions. I also thank Prof. Michael O'Boyle and Dr. Robert Mullins for being on my viva panel and making it a memorable experience. I thank several members of ICSA who provided valuable feedback, suggestions and a space to improve my ideas. I would like to specially thank Arpit Joshi, Cheng-Chieh Huang, José Cano Reyes, Marco Elver, Priyank Faldu and Rakesh Kumar for their valuable help and support, both technical and otherwise. I also thank several anonymous reviewers from the Computer Architecture community who provided valuable feedback and suggestions, which was crucial in improving my work. Furthermore, I am grateful for the School of Informatics PhD Scholarship and Saranu International Research Scholarship in enabling my PhD study.

I would like to thank all my friends who offered me their joyous company during my time in Edinburgh. Their friendship helped me cruise through the years of my graduate studies, and made each and every moment spent here memorable.

Finally, I would like to express my profound gratitude to my parents, Geeta Dublish and Rajeev Dublish, for providing me with the values, guidance and unwavering support throughout my life. It is difficult to imagine reaching this juncture without their enormous love and sacrifices. I also thank my brother, Tushar Dublish, for his incredible support and assistance throughout my graduate studies.

## **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified.

(Saumay Dublish)

Dedicated to my parents

# **Table of Contents**

| 1 | Intr | oductio       | on                                            | 1  |

|---|------|---------------|-----------------------------------------------|----|

|   | 1.1  | The Pa        | roblem                                        | 2  |

|   |      | 1.1.1         | Inadequate Bandwidth Resources                | 2  |

|   |      | 1.1.2         | Poor Cache Management                         | 3  |

|   |      | 1.1.3         | High Thread-level Parallelism                 | 4  |

|   |      | 1.1.4         | Implications of Bandwidth Bottlenecks         | 4  |

|   |      | 1.1.5         | Summary                                       | 5  |

|   | 1.2  | Contri        | ibutions                                      | 5  |

|   |      | 1.2.1         | Cost-effective Scaling of Bandwidth Resources | 6  |

|   |      | 1.2.2         | Cooperative Caching for L1 Caches             | 6  |

|   |      | 1.2.3         | Managing Thread-level Parallelism             | 7  |

|   |      | 1.2.4         | Summary                                       | 7  |

|   | 1.3  | Publis        | hed Work                                      | 9  |

|   | 1.4  | Organ         | ization                                       | 9  |

| 2 | GPU  | U <b>Comp</b> | outing                                        | 11 |

|   | 2.1  | Progra        | amming Model                                  | 12 |

|   | 2.2  | GPU A         | Architecture                                  | 14 |

|   |      | 2.2.1         | Warp Scheduling                               | 15 |

|   |      | 2.2.2         | GPU Memory Hierarchy                          | 16 |

|   |      | 2.2.3         | Memory Coalescing                             | 19 |

| 3 | Eva  | luating       | and Mitigating Bandwidth Bottlenecks          | 21 |

|   | 3.1  | Overv         | iew                                           | 21 |

|   | 3.2  | Backg         | ground                                        | 24 |

|   |      | 3.2.1         | Baseline Architecture                         | 24 |

|   |      | 3.2.2         | Simulation Framework                          | 24 |

|   |     | 3.2.3            | Workloads                                 | 25 |

|---|-----|------------------|-------------------------------------------|----|

|   | 3.3 | Motiva           | ation                                     | 26 |

|   |     | 3.3.1            | Limits of Latency Tolerance in GPUs       | 26 |

|   |     | 3.3.2            | Performance Impact of Reducing Congestion | 27 |

|   | 3.4 | Dissec           | eting the Bandwidth Bottleneck            | 28 |

|   |     | 3.4.1            | Implications of Congestion                | 29 |

|   |     | 3.4.2            | Causes of Congestion                      | 33 |

|   | 3.5 | Conso            | lidating the Design Space                 | 35 |

|   |     | 3.5.1            | Off-chip Memory                           | 36 |

|   |     | 3.5.2            | L2 Cache                                  | 37 |

|   |     | 3.5.3            | L1 Cache                                  | 37 |

|   | 3.6 | Design           | n Space Exploration                       | 37 |

|   |     | 3.6.1            | Results                                   | 38 |

|   |     | 3.6.2            | Summary                                   | 40 |

|   | 3.7 | Cost-E           | Benefit Analysis                          | 41 |

|   |     | 3.7.1            | Cost-effective Design Space               | 41 |

|   |     | 3.7.2            | Asymmetric Crossbar                       | 42 |

|   |     | 3.7.3            | Results with Cost-effective Configuration | 42 |

|   | 3.8 | Relate           | d Work                                    | 43 |

|   |     | 3.8.1            | Cache Bypassing and Request Reordering    | 43 |

|   |     | 3.8.2            | On-chip Networks in GPUs                  | 46 |

|   |     | 3.8.3            | Design Space Exploration                  | 47 |

|   | 3.9 | Conclu           | usion                                     | 48 |

| 4 | Coo | nerativ <i>i</i> | e Caching for GPUs                        | 50 |

| • | 4.1 | •                | iew                                       | 50 |

|   | 4.2 |                  | round                                     | 53 |

|   |     | 4.2.1            | Baseline Architecture                     | 53 |

|   |     | 4.2.2            | Workloads                                 | 55 |

|   | 4.3 |                  | for Cooperation                           | 55 |

|   |     | 4.3.1            | Inter-core Reuse                          | 56 |

|   |     | 4.3.2            | Efficacy of Cooperation                   | 57 |

|   | 4.4 |                  | erative Caching                           | 58 |

|   |     | 4.4.1            | Analytical Model                          | 59 |

|   |     | 4.4.2            | Architecture                              | 60 |

|   |     | <del></del>      |                                           |    |

|   |     | 4.4.3   | Shadow Tags                          |

|---|-----|---------|--------------------------------------|

|   |     | 4.4.4   | Request Throttler                    |

|   |     | 4.4.5   | Working Example                      |

|   | 4.5 | Evalua  | ntion                                |

|   |     | 4.5.1   | Implementation                       |

|   |     | 4.5.2   | Experimental Setup                   |

|   |     | 4.5.3   | Results                              |

|   |     | 4.5.4   | Hardware Cost                        |

|   |     | 4.5.5   | Sensitivity Analysis                 |

|   |     | 4.5.6   | Discussion                           |

|   | 4.6 | Compa   | arative Study                        |

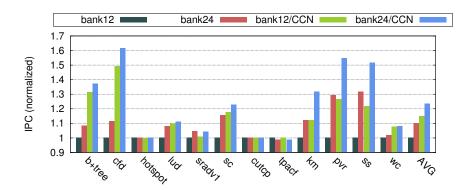

|   |     | 4.6.1   | Increasing L2 Banks                  |

|   |     | 4.6.2   | Sharing Tracker                      |

|   |     | 4.6.3   | Clustered Sharing                    |

|   |     | 4.6.4   | Summary                              |

|   | 4.7 | Relate  | d Work                               |

|   |     | 4.7.1   | Cooperative Caching in CMPs          |

|   |     | 4.7.2   | Ring Network                         |

|   |     | 4.7.3   | Shadow Tags                          |

|   |     | 4.7.4   | Cache Management                     |

|   |     | 4.7.5   | Thread Block Scheduling              |

|   | 4.8 | Conclu  | asion                                |

| 5 | Man | aging T | Thread-level Parallelism 83          |

|   | 5.1 | Overvi  | iew                                  |

|   | 5.2 | Backg   | round                                |

|   |     | 5.2.1   | Baseline Architecture                |

|   |     | 5.2.2   | Supervised Learning                  |

|   | 5.3 | Motiva  | ation                                |

|   |     | 5.3.1   | Cache-Conscious Wavefront Scheduling |

|   |     | 5.3.2   | Priority-based Cache Allocation      |

|   |     | 5.3.3   | Pitfalls in Prior Techniques         |

|   |     | 5.3.4   | Summary                              |

|   | 5.4 | Poise:  | A System Overview                    |

|   | 5 5 | Machi   | ne Learning Framework                |

|   |     | 5.5.1   | Analytical Model                             | )2  |

|---|-----|---------|----------------------------------------------|-----|

|   |     | 5.5.2   | Feature Vector Representation                | 7   |

|   |     | 5.5.3   | Training Methodology                         | )1  |

|   |     | 5.5.4   | Regression Model                             | )2  |

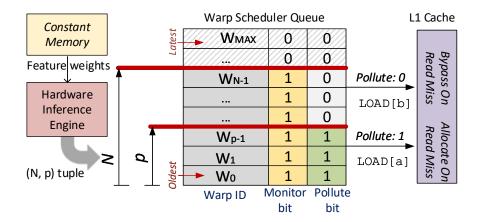

|   | 5.6 | Hardw   | are Inference Engine                         | )3  |

|   |     | 5.6.1   | Prediction Stage                             | )3  |

|   |     | 5.6.2   | Correction Stage                             | )4  |

|   |     | 5.6.3   | Warp Scheduler                               | )5  |

|   |     | 5.6.4   | Summary                                      | )6  |

|   | 5.7 | Evalua  | tion                                         | )6  |

|   |     | 5.7.1   | Workloads                                    | )6  |

|   |     | 5.7.2   | Regression Model Evaluation                  | )6  |

|   |     | 5.7.3   | Experimental Methodology                     | )8  |

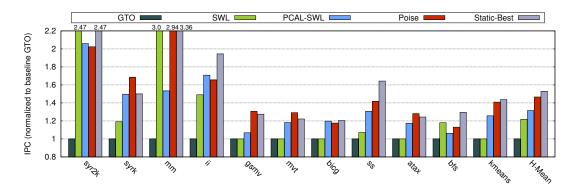

|   |     | 5.7.4   | Performance                                  | )9  |

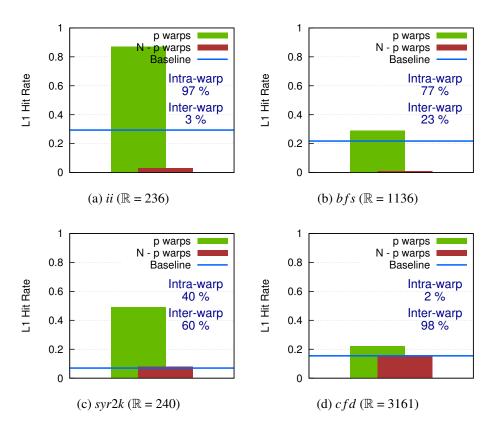

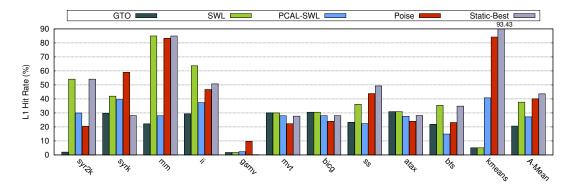

|   |     | 5.7.5   | L1 Cache Hit Rate                            | 0   |

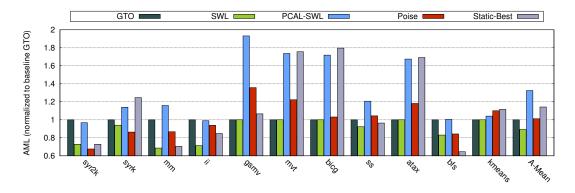

|   |     | 5.7.6   | Average Memory Latency                       | .0  |

|   |     | 5.7.7   | Sensitivity Study                            | l 1 |

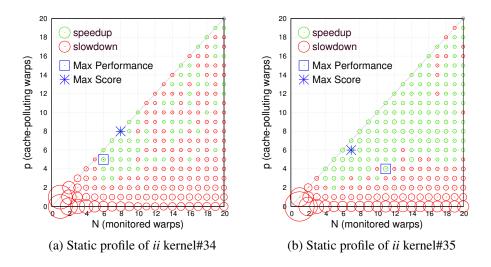

|   |     | 5.7.8   | Case Study                                   | 3   |

|   |     | 5.7.9   | Hardware Overheads                           | .4  |

|   |     | 5.7.10  | Discussion                                   | 5   |

|   | 5.8 | Related | d Work                                       | .5  |

|   |     | 5.8.1   | Cache Management and Warp Scheduling         | .5  |

|   |     | 5.8.2   | Machine Learning in Systems                  | 17  |

|   | 5.9 | Conclu  | sion                                         | .8  |

| 6 | Con | clusion | 12                                           | 20  |

|   | 6.1 | Contril | outions                                      | 20  |

|   |     | 6.1.1   | Scaling the Bandwidth Resources              | 21  |

|   |     | 6.1.2   | Supplementing the Bandwidth Resources        | 21  |

|   |     | 6.1.3   | Utilizing the Bandwidth Resources            | 22  |

|   | 6.2 | Critica | l Analysis                                   | 22  |

|   |     | 6.2.1   | Ease of Adoption                             | 23  |

|   |     | 6.2.2   | Portability                                  | 24  |

|   |     | 6.2.3   | Evaluation Methodology                       | 24  |

|   |     | 6.2.4   | Other Inefficiencies in the Memory Hierarchy | 25  |

| Bibliography    |                 |                 |                 |                 | 128             |                 |                 |                 |                 |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| cluding Remarks |                 |                 |                 |                 |                 |                 |                 |                 | 127             |

| re Work         |                 |                 |                 |                 |                 |                 |                 |                 | 125             |

| (               | cluding Remarks |

# **List of Figures**

| 1.1  | Typical bandwidth hierarchy in GPUs                                         | 3  |

|------|-----------------------------------------------------------------------------|----|

| 1.2  | Proposed three-pronged approach to address the bandwidth bottlenecks        |    |

|      | across the memory hierarchy in GPUs. Bandwidth demand is repre-             |    |

|      | sented by blue arrows; reduction in bandwidth demand is represented         |    |

|      | by crossed red arrows; and scaled or additional bandwidth resources         |    |

|      | are represented by red blocks                                               | 8  |

| 2.1  | CUDA program structure                                                      | 12 |

| 2.2  | System-level architecture of a typical GPU                                  | 15 |

| 2.3  | Baseline GPU architecture                                                   | 16 |

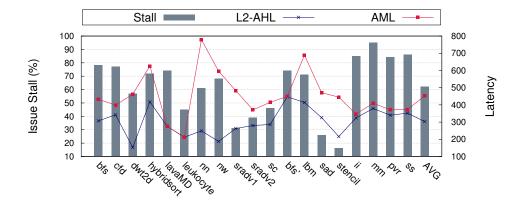

| 3.1  | Issue-stall cycles, Average Hit Latencies to L2 (L2-AHL) and Average        |    |

|      | Memory Latencies (AML) for memory-intensive applications                    | 22 |

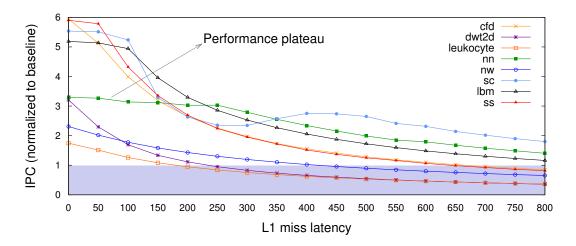

| 3.2  | Performance variation with increasing L1 miss latency                       | 26 |

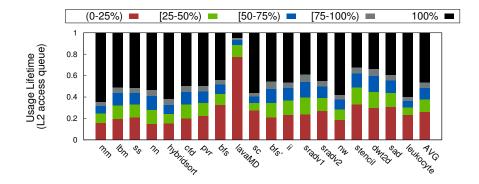

| 3.3  | Occupancy levels in L2 access queue during the usage lifetime               | 28 |

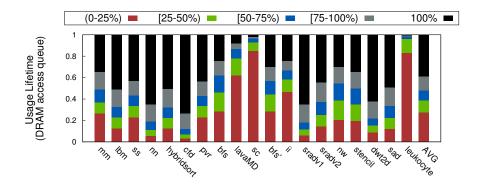

| 3.4  | Occupancy levels in DRAM access queue during the usage lifetime .           | 29 |

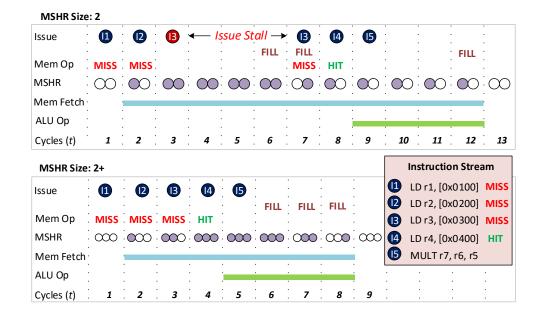

| 3.5  | Illustrating the effects of structural hazards                              | 31 |

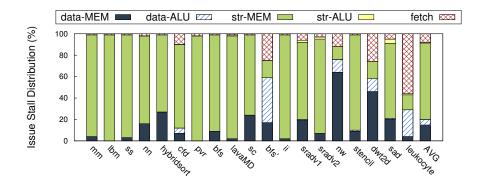

| 3.6  | Issue-stall cycle distribution depicting stalls due to data hazards (data-  |    |

|      | MEM and data-ALU), structural hazards (str-MEM and str-ALU) and             |    |

|      | fetch hazard (fetch)                                                        | 32 |

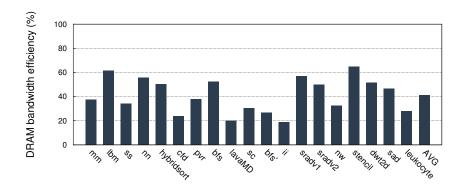

| 3.7  | DRAM bandwidth efficiency                                                   | 33 |

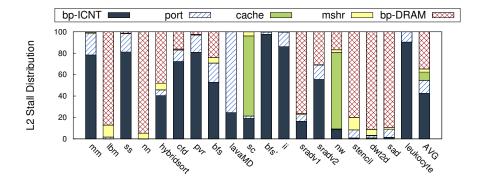

| 3.8  | L2 stalls due to back pressure from interconnect (bp-ICNT) and DRAM         |    |

|      | (bp-DRAM) and contention on L2 data port, cache lines and MSHRs.            | 34 |

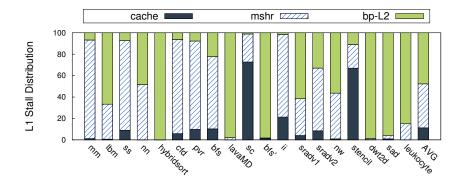

| 3.9  | L1 stalls due to contention on cache lines and MSHRs, and back pres-        |    |

|      | sure from L2 cache (bp-L2)                                                  | 35 |

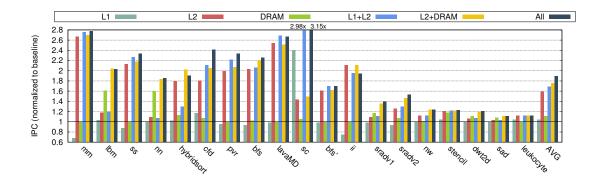

| 3.10 | IPC gain with $4 \times$ design-point scaling of bandwidth resources in L1, |    |

|      | L2, DRAM and synergistically across different levels                        | 38 |

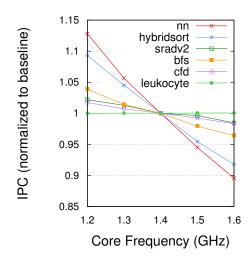

| 3.11 | Core frequency variation on real GTX 480 GPU                                | 39 |

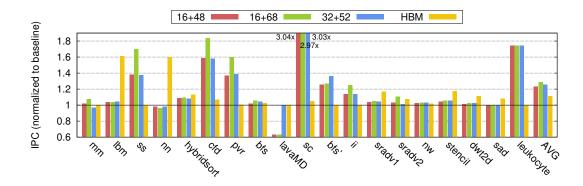

| 3.12 | ing or equal cost overheads, normalized to the baseline architecture         | 42  |

|------|------------------------------------------------------------------------------|-----|

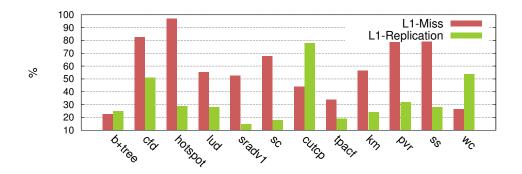

| 4.1  | (a) L1-Miss: L1 cache miss rates (b) L1-Replication: Percentage of L1        |     |

|      | misses cached in remote L1 caches                                            | 51  |

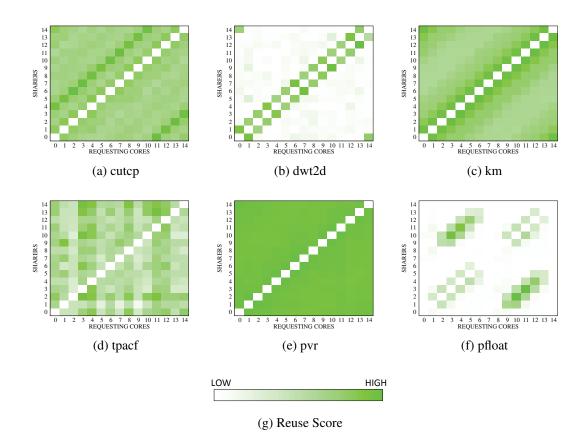

| 4.2  | Heatmaps indicating inter-core reuse by cores on the <i>x</i> -axis for data |     |

|      | cached on the cores on the y-axis. Dark spots in the heatmaps indicate       |     |

|      | high reuse between the corresponding cores at their $x$ and $y$ coordinates. | 56  |

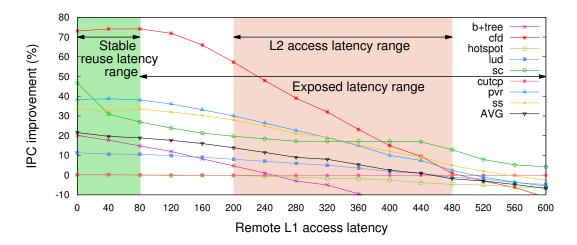

| 4.3  | Speedup of cooperation with varying remote L1 access latencies               | 58  |

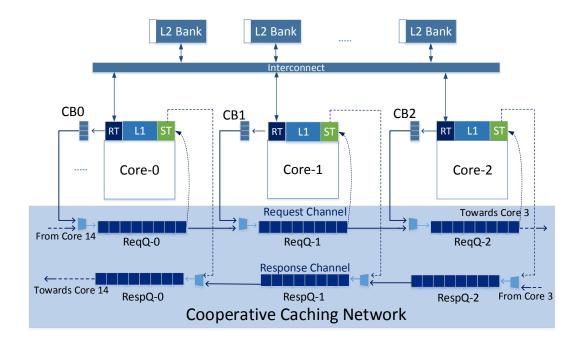

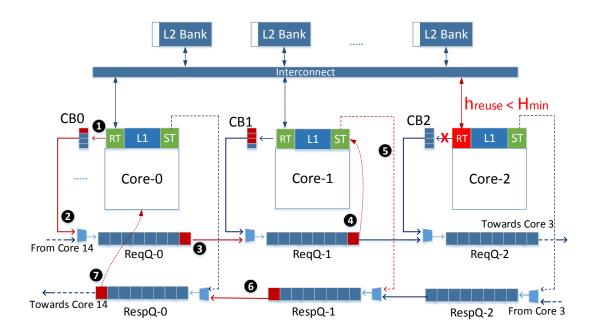

| 4.4  | Cooperative Caching Network                                                  | 60  |

| 4.5  | Working of the Cooperative Caching Network with Request Throttling.          | 65  |

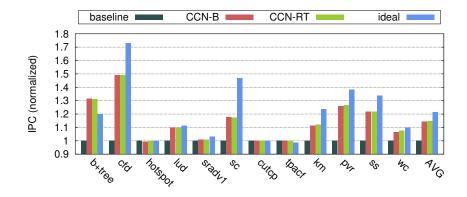

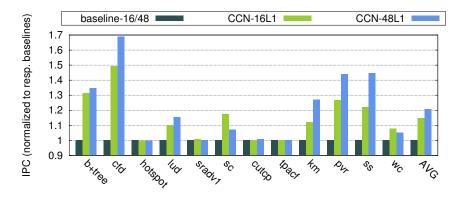

| 4.6  | Speedup for applications with $\mu RC > 10 \dots \dots \dots$                | 67  |

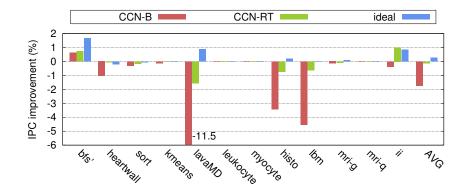

| 4.7  | Percentage improvement in IPC for applications with $\mu RC < 3$             | 67  |

| 4.8  | Percentage reduction in L1 to L2 traffic                                     | 68  |

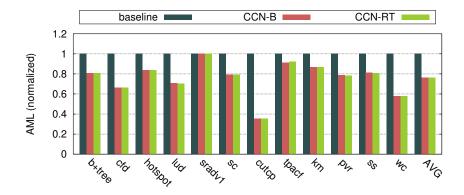

| 4.9  | Normalized average memory latency                                            | 69  |

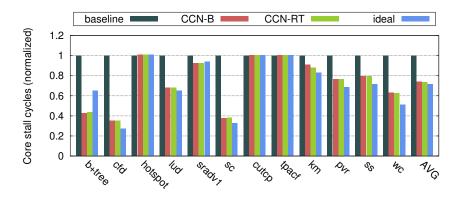

| 4.10 | Normalized core stall cycles                                                 | 69  |

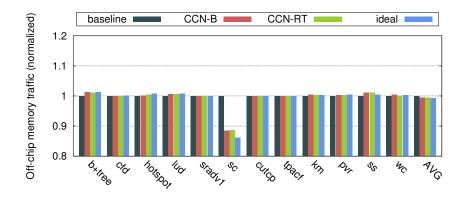

| 4.11 | Normalized off-chip memory traffic                                           | 70  |

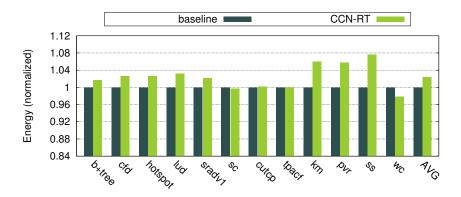

| 4.12 | Energy dissipation with CCN                                                  | 71  |

| 4.13 | Speedup with varying L1 cache size                                           | 71  |

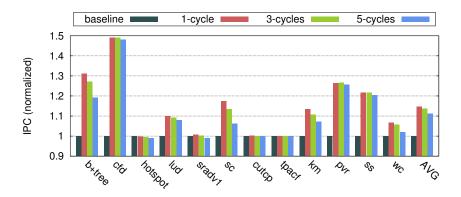

| 4.14 | Speedup with link latencies of 1, 3 and 5 cycles                             | 72  |

| 4.15 | Speedup with varying SIMD lanes                                              | 73  |

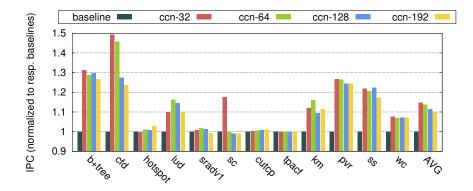

| 4.16 | Speedup with $2 \times L2$ banks and CCN                                     | 74  |

| 4.17 | Ideal speedup with L1 cache clusters                                         | 76  |

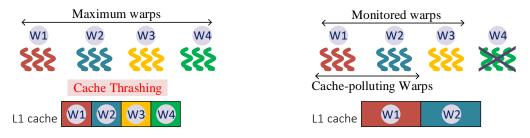

| 5.1  | Cache footprint with maximum warps and reduced warps                         | 84  |

| 5.2  | Static profiling of ii kernel #112                                           | 89  |

| 5.3  | System-level architecture of <i>Poise</i>                                    | 91  |

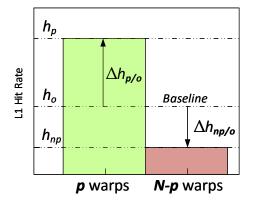

| 5.4  | L1 hit rate comparison for $p$ and $N-p$ warps                               | 94  |

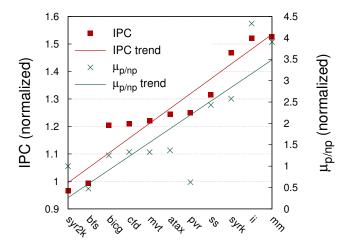

| 5.5  | Correlation between speedup and $\mu_{p/np}$ with $p=1$ and $N=24$           | 96  |

| 5.6  | L1 hit rate distribution                                                     | 99  |

| 5.7  | Scoring performance peaks to avoid cliffs                                    | 102 |

| 5.8  | Poise Warp Scheduler architecture                                            | 105 |

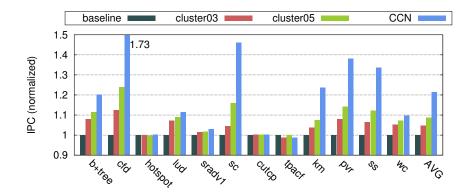

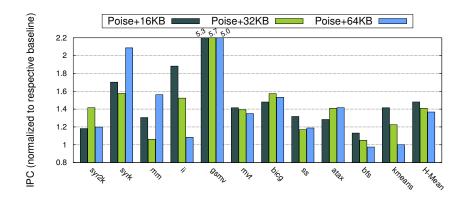

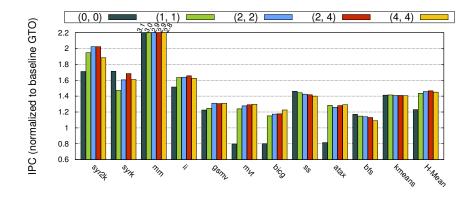

| 5.9  | Performance normalized to GTO                                                | 109 |

| 5.10 | Overall L1 hit rate                                                          | 110 |

| 5.11 | Average Memory Latency (AML) normalized to GTO                               | 110 |

| 5 12 | Sensitivity to L1 cache size                                                 | 111 |

| 5.13 | Sensitivity to search stride $(\varepsilon_N, \varepsilon_p)$ | 112 |

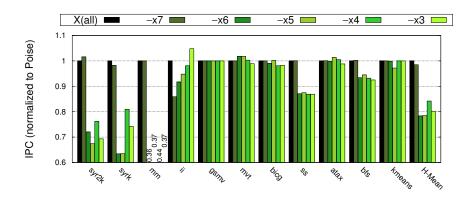

|------|---------------------------------------------------------------|-----|

| 5.14 | Sensitivity to removing a feature $x_i$ from X                | 112 |

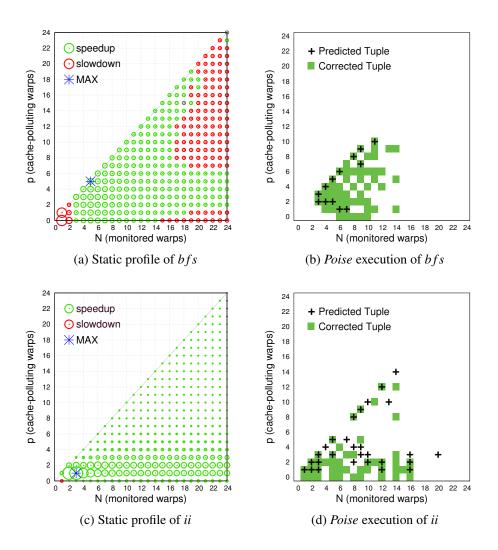

| 5.15 | Comparing static and <i>Poise</i> executions                  | 113 |

# **List of Tables**

| 3.1 | Baseline architecture parameters for GPGPU-Sim                                      | 24  |

|-----|-------------------------------------------------------------------------------------|-----|

| 3.2 | List of workloads. $P_{\infty}$ : Speedup with infinite bandwidth memory sys-       |     |

|     | tem; P <sub>DRAM</sub> : Speedup with a baseline cache hierarchy and infinite band- |     |

|     | width DRAM                                                                          | 25  |

| 3.3 | Consolidated design space showing baseline, scaled (4×) and cost-                   |     |

|     | effective configurations                                                            | 36  |

| 4.1 | Baseline architectural parameters for GPGPU-Sim                                     | 53  |

| 4.2 | Benchmark characterization: (a) PerfX - speedup with perfect memory                 |     |

|     | (b) $\mu$ RC - percentage of total L1 load misses that have reusable data on        |     |

|     | a remote L1                                                                         | 54  |

| 4.3 | CCN parameters                                                                      | 66  |

| 5.1 | Baseline architecture parameters for GPGPU-Sim                                      | 86  |

| 5.2 | Variables derived from the analytical model                                         | 98  |

| 5.3 | Feature Vector (X) and Feature Weights $(\alpha; \beta)$                            | 100 |

| 5.4 | Training and evaluation workloads                                                   | 107 |

| 5.5 | Poise parameters                                                                    | 107 |

| 6.1 | Relative overhead of adoption for the proposed schemes indicated by H               |     |

|     | (highest), M (moderate) and L (lowest)                                              | 124 |

# **Chapter 1**

## Introduction

In the past decade, the journey of GPUs in transforming the computing landscape has been phenomenal. Initially used to render graphics for computer games, GPUs are now at the centre of major advancements in areas ranging from artificial intelligence to enterprise computing. As a result, GPUs have proven to be of substantive significance in the world of general-purpose computing, emerging as a formidable alternative to traditional single-threaded processors.

Wide contrast in the performance of CPUs and GPUs derives from a fundamental difference in the design philosophies of these architectures. CPUs are heavily optimized for single-threaded performance, dedicating a substantial portion of the die area to storage units, such as caches, for faster data access. In contrast, GPUs are heavily multithreaded and dedicate most of the die area to compute units, making them more tolerant to memory latencies of individual threads. In such multithreaded architectures, however, memory bandwidth poses a much bigger challenge as high levels of multithreading present a high demand on the off-chip memory bandwidth. This has led to the introduction of deeper memory hierarchies in modern GPUs, comprising multilevel caches, to filter the bandwidth demand to off-chip memory. However, compared to CPUs, the cache hierarchy in GPUs encounter significantly different demands and bottlenecks due to considerably higher volumes of memory traffic. As a result, the adoption of conventional cache hierarchy in GPUs has triggered significant research efforts to address these new bottlenecks and to ensure a well performing memory system, which is crucial for the future success of GPUs.

#### 1.1 The Problem

The caches in GPUs are much smaller in comparison to CPU caches, in line with the throughput-oriented nature of GPUs. For instance, Intel's Haswell processor [55] features over 8 MB of on-chip memory that is shared by a handful of threads. In contrast, NVIDIA's Kepler GPU [116] features only around 2 MB of on-chip memory that is shared by tens of thousands of threads. Consequently, small caches and large number of threads in GPUs can lead to high cache miss rates and cache thrashing [66, 67, 132]. Due to poor cache performance, the cache hierarchy does not adequately filter the bandwidth demand to off-chip memory. In addition, the cache hierarchy exposes its own bandwidth limitations in sustaining such high levels of memory traffic [139]. As a result, the bandwidth implications of the entire memory hierarchy, including caches, pose a severe challenge to GPU performance and warrants investigation [76]. In the remainder of this section, we briefly present the principal factors that lead to bandwidth bottlenecks across the memory hierarchy in GPUs and discuss their performance implications. Later, in subsequent chapters, we delve into more details about these challenges.

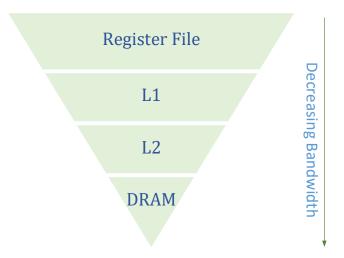

#### 1.1.1 Inadequate Bandwidth Resources

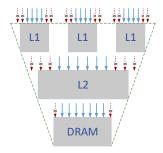

A typical memory hierarchy comprises small and fast first-level caches closest to the processors, and progressively larger and slower caches at the lower levels of the memory hierarchy. The aggregate bandwidth provided by each memory level also tapers as we go lower in the memory hierarchy, and is depicted by the *bandwidth pyramid* in Figure 1.1. This is because each level filters the bandwidth demand to the lower level, and consequently the lower levels require only a fraction of bandwidth of the higher levels. Therefore, appropriate allocation of bandwidth resources to each level of the memory hierarchy, *i.e.*, shaping the bandwidth pyramid, is critical for a well-performing memory system.

In GPUs, the off-chip bandwidth continues to scale with upcoming memory technologies such as High Bandwidth Memories (HBM), providing high bandwidth to inject memory responses into the cache hierarchy. In addition, the number of GPU cores continue to grow, increasing the bandwidth demand on the cache hierarchy. However, the conventional cache hierarchy adopted by GPUs is under-provisioned in bandwidth resources (such as on-chip interconnect, peripheral buffers, *etc.*) to handle such high volumes of memory traffic. As a result, the bandwidth hierarchy is becoming increasingly imbalanced, leading to growing congestion across the memory hierarchy — specifically

Figure 1.1: Typical bandwidth hierarchy in GPUs

the caches. Therefore, a key challenge is to investigate the distribution of bandwidth demand and the resultant bottlenecks across the memory hierarchy in GPUs, and evaluate the design space to provision the cache hierarchy with appropriate bandwidth resources, thereby mitigating the bandwidth bottlenecks.

#### 1.1.2 Poor Cache Management

Typically, GPUs exhibit high cache miss rates, indicating that the cache performance is far from perfect. This is partly because current GPU cache management techniques are unable to utilize these caches effectively. One such inefficiency in current GPU cache management policies is the repeated access to the shared L2 cache from different L1 caches for the same data, arising due to inter-core data reuse. Such a policy is a common occurrence in CPUs and is generally benign for performance when L1 miss rates are low. In such cases, it does not excessively deplete the memory bandwidth. In GPUs, however, such a policy is corrosive to the overall performance due to high L1 miss rates. As a result, for memory-intensive applications, where performance is constrained by memory bandwidth, such a policy aggravates the bandwidth issue by repeated memory requests for data already cached elsewhere at the same level in the memory hierarchy. Evidently, the policies that are suitable for CPUs may not be suitable for GPUs. Therefore, it is critical to address the inefficiencies of the existing cache management policies in GPUs to ensure effective usage of scarce bandwidth resources. Notably, the inefficient usage of caches in GPUs is even more alarming considering that the die area they occupy might otherwise be used to implement additional GPU

cores, which arguably hold much more importance to throughput-oriented computing systems. For this to be an effective trade-off, the efficiency of the cache hierarchy must be maximized.

#### 1.1.3 High Thread-level Parallelism

GPUs employ a Single-Instruction Multiple-Threads (SIMT) execution model, which requires a large number of threads to execute a set of similar instructions. Due to the abundance of parallel work available in such systems, set of threads that encounter a long latency memory operation are replaced by another set of threads that are ready to resume execution, while the pending memory operations are completed. Therefore, GPUs rely on a high degree of thread-level parallelism (via multithreading) to hide the long latency of memory operations. Often, in compute-intensive applications where long latency memory operations are infrequent, increasing the number of threads available for multithreading continues to improve the latency hiding ability of GPUs. However, in memory-intensive applications where memory instructions account for a significant fraction of the total instructions, increasing the number of threads often leads to a considerable increase in demand for memory resources such as caches and memory bandwidth. Consequently, the high demand for memory resources overwhelms the memory hierarchy and leads to poor memory system performance, giving rise to problems such as cache thrashing and bandwidth bottlenecks. As a result, these side-effects adversely affect system performance, thereby diminishing the benefits of parallelism.

The problems of cache thrashing and bandwidth bottlenecks can be mitigated by reducing the level of multithreading in the GPUs. However, the optimal level of multithreading may vary significantly across different applications and architectures, and therefore naively restricting multithreading can adversely affect throughput. Due to this tension between *thread-level parallelism* and *memory system performance*, and its direct impact on cache performance and bandwidth demand, balancing these two properties poses a significant challenge.

#### 1.1.4 Implications of Bandwidth Bottlenecks

Due to the bandwidth bottlenecks arising out of the above challenges, there can be severe congestion across the memory hierarchy in GPUs. Such high levels of congestion lead to increased average memory latencies, and this has three major implications. Firstly, in

memory-intensive applications, due to insufficient computation to mask high memory latencies, such latencies appear in the critical path of system performance. Secondly, high latencies of outstanding miss requests lead to prolonged contention for cache resources such as Miss Status Holding Registers (MSHRs) and replaceable cache lines. This effect increases memory latencies even further, as succeeding requests get serialized and have to wait for outstanding misses to complete and relinquish the resources. And thirdly, back pressure from a congested lower level further throttles the cache pipeline and prevents it from operating at peak throughput, exacerbating the bandwidth limitation in the cache hierarchy. The combination of the above factors forces the cores to stall, leading to performance degradation.

#### 1.1.5 Summary

In summary, we identify that the bandwidth bottleneck across the memory hierarchy is a significant problem in modern GPUs; this is the key issue that we address in this thesis. There are three principal factors that lead to bandwidth bottlenecks: firstly, the growing bandwidth imbalance in the memory hierarchy; secondly, inefficient cache management; and thirdly, high levels of thread-level parallelism. In memory-intensive applications, these factors lead to high congestion in the memory hierarchy, thereby adversely impacting performance.

#### 1.2 Contributions

In this thesis, we propose the following three-pronged approach to address the bandwidth bottlenecks arising out of the issues discussed in the previous section. Firstly, we characterize the memory hierarchy with respect to the bandwidth bottlenecks and propose cost-effective scaling of bandwidth resources. Secondly, we propose a cooperative caching mechanism for L1 caches to improve the caching efficiency in GPUs with respect to the bandwidth demand on the lower levels. And thirdly, we propose a machine learning technique to adaptively balance thread-level parallelism and memory system performance. We discuss these strategies briefly in the remainder of this section, followed by detailed evaluation and discussion in the subsequent chapters.

#### 1.2.1 Cost-effective Scaling of Bandwidth Resources

In this proposal (detailed in Chapter 3), we address the challenge of rising imbalance in the bandwidth hierarchy in GPUs, which is discussed in Section 1.1.1. We characterize the bandwidth bottlenecks present across the memory hierarchy in GPUs and quantify the stalls throughout the memory hierarchy. We use this characterization to identify the architectural parameters that are most critical in alleviating congestion. We explore the architectural design space to mitigate the bandwidth bottlenecks and show that the performance improvement achieved by mitigating the bandwidth bottleneck in the cache hierarchy can exceed the speedup obtained by a memory system with a baseline cache hierarchy and High Bandwidth Memory (HBM) DRAM. This signifies the importance of resolving bandwidth bottlenecks in the cache hierarchy, in comparison to simply increasing off-chip memory bandwidth.

We also show that addressing the bandwidth bottleneck in isolation, at specific levels, can be sub-optimal and can even be counter-productive. Therefore, we show that it is imperative to resolve the bandwidth bottlenecks synergistically across different levels of the memory hierarchy. With the insights developed in this proposal, we perform a cost-benefit analysis and identify cost-effective configurations of the memory hierarchy that effectively mitigate the bandwidth bottlenecks. We conclude this study by presenting a cost-effective configuration that comprises an asymmetric crossbar alongside scaled peripheral resources such as buffers and MSHRs. We show that our final configuration achieves a performance improvement of 29% on average, with a minimal area overhead of 1.5%, compared to the baseline modern GPU.

#### 1.2.2 Cooperative Caching for L1 Caches

In this proposal (detailed in Chapter 4), we aim to address an inefficiency in the traditional cache management techniques, which is discussed in Section 1.1.2. We identify significant data reuse across different GPU cores, presenting an opportunity to reuse data among the L1 caches. By sharing data among L1s, we aim to reduce the pressure on the shared L2 bandwidth, thereby reducing the memory access latencies that lie in the critical path. We show how data reuse can be exploited via an L1 Cooperative Caching Network (CCN), thereby supplementing the existing bandwidth resources and reducing demand on the shared L2 bandwidth. In the proposed architecture, we connect the L1 caches with a lightweight ring network to facilitate inter-core communication of shared data. We show that this technique reduces traffic to the L2 cache by an average

of 29%, freeing up the shared L2 bandwidth for other accesses. We also show that CCN reduces the average memory latency by 24%, thereby reducing core stall cycles by 26% on average. This translates into an overall performance improvement of 14.7% on average (and up to 49%) for applications that exhibit reuse across L1 caches. In doing so, CCN incurs a nominal area and energy overhead of 1.3% and 2.5% respectively. Notably, the performance improvement with our proposed CCN compares favourably to the performance improvement achieved by simply doubling the number of L2 banks by up to 34%.

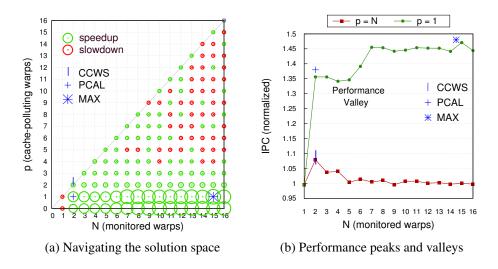

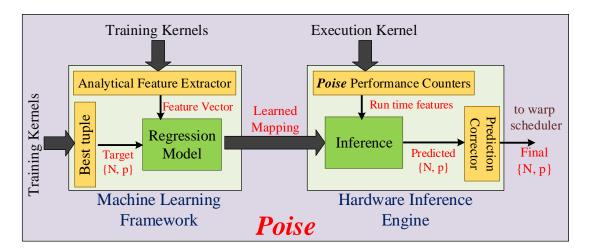

#### 1.2.3 Managing Thread-level Parallelism

In this proposal (detailed in Chapter 5), we address the adverse effect of high thread-level parallelism on memory system performance, which is discussed in Section 1.1.3. We present *Poise*, a novel approach that alters the warp scheduling mechanism in the GPU to balance thread-level parallelism and memory system performance. *Poise* achieves this by adding a set of two knobs to the warp scheduler. The first knob determines the number of warps that can pollute the cache in order to improve memory system performance, while the second knob determines the overall thread-level parallelism in order to maximize the multithreading available in the system. *Poise* determines these warp scheduling decisions using the following two major components: a machine learning framework and a hardware inference engine. The machine learning framework comprises a supervised learning model that is trained offline on a large set of profiled kernels to make good warp scheduling decisions. This is achieved by learning a mapping from a set of application and architectural features, to the warp scheduling decisions that led to the best performance for a kernel. At runtime, the hardware inference engine collects these features periodically using hardware performance counters, and uses the mapping that was learned during training to dynamically predict good warp scheduling decisions. As a result, *Poise* achieves a performance improvement of up to 2.94× and a harmonic mean speedup of 46.6%, over the baseline greedy-then-oldest warp scheduler. It also outperforms the prior state-of-the-art warp scheduler by an average of 15.1%, while incurring minimal hardware overheads in contrast to prior techniques.

#### 1.2.4 Summary

In this thesis, we investigate the bandwidth implications of the different levels of the memory hierarchy and demonstrate how the current policies breach the latency tolerance

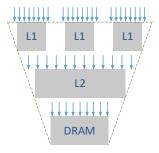

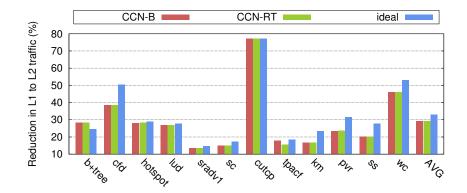

(a) Baseline bandwidth hierarchy when high bandwidth demand causes a bottleneck.

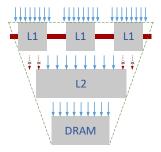

(c) *Supplementing* the existing bandwidth resources in the cache hierarchy.

(b) *Scaling* the existing bandwidth resources in the cache hierarchy.

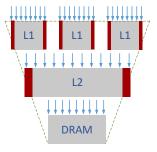

(d) *Utilizing* the existing bandwidth resources by reducing the bandwidth demand.

Figure 1.2: Proposed three-pronged approach to address the bandwidth bottlenecks across the memory hierarchy in GPUs. Bandwidth demand is represented by *blue arrows*; reduction in bandwidth demand is represented by crossed *red arrows*; and scaled or additional bandwidth resources are represented by *red blocks*.

property of GPUs by causing congestion across the memory hierarchy. The baseline bandwidth hierarchy is represented in Figure 1.2a where high demand on the memory hierarchy leads to a bandwidth bottleneck. Note that we omit register files from the discussion as they are often underutilized for general-purpose applications [1, 121] and are seldom a bandwidth bottleneck. We propose a three-pronged approach to address the problem. Firstly, we investigate how to *best scale the existing bandwidth resources* in the GPU through characterization and design space exploration (Figure 1.2b). Secondly, we investigate how to *best supplement the existing bandwidth resources* through a cooperative caching network for L1 caches (Figure 1.2c). And thirdly, we investigate how to *best utilize the existing bandwidth resources* by balancing thread-level parallelism and memory system performance (Figure 1.2d).

#### 1.3 Published Work

Some of the contents of this thesis have appeared in the following publications:

- S. Dublish, *Student Research Poster: Slack-Aware Shared Bandwidth Management in GPUs*, ACM SRC, The 25th International Conference on Parallel Architectures and Compilation Techniques (PACT), Haifa, Israel, September 11-15, 2016.

- Appears in *Chapter 6 (Section 6.3)*.

- S. Dublish, V. Nagarajan and N. Topham, *Characterizing Memory Bottlenecks in GPGPU Workloads*, IEEE International Symposium on Workload Characterization (IISWC), Providence, Rhoda Island, USA, September 25-27, 2016.

- Appears in *Chapter 3*.

- S. Dublish, V. Nagarajan and N. Topham, *Cooperative Caching for GPUs*, ACM Transactions on Architecture and Code Optimization (TACO), 13(4), 39, December 2016.

- Appears in *Chapter 4*.

- S. Dublish, V. Nagarajan and N. Topham, *Evaluating and Mitigating Bandwidth Bottlenecks Across the Memory Hierarchy in GPUs*, IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), Santa Rosa, USA, April 23-25, 2017.

- Appears in *Chapter 3*.

## 1.4 Organization

The remainder of this thesis is organized as follows: Chapter 2 provides a background about GPU computing. Chapter 3 presents a characterization of bandwidth bottlenecks in the memory hierarchy of GPUs and evaluates the design space for cost-effective scaling of the bandwidth resources. Chapter 4 evaluates the reuse patterns for general-purpose applications and presents CCN, a Cooperative Caching Network for L1 caches in GPUs. Chapter 5 presents *Poise*, a warp scheduling policy to balance multithreading and memory system performance, consequently lowering the demand for shared

10

bandwidth resources in the memory hierarchy. Chapter 6 concludes the thesis by summarizing the findings and contributions of this work as well as exploring the scope for future work.

# **Chapter 2**

# **GPU Computing**

Consumer graphics hardware started gaining attention as early as the 1980s — at the time used primarily in arcade and console gaming devices. In the initial years, industry efforts were focused towards enabling 2D graphics through a variety of video cards and graphic adaptors [29, 48, 156]. Later, during the 1990s, further progress in the graphics industry ushered in an era of 3D graphics and revolutionized computer graphics. Throughout that decade, graphics hardware companies such as ATI (now acquired by AMD), 3Dfx and NVIDIA dominated most of the consumer graphics industry. With the turn of the century, NVIDIA introduced GeForce 256 [42] — the first commercially available Graphics Processing Unit or GPU. In 2006, after a series of architectural revamps and modifications, NVIDIA introduced the G80 series GPUs. It featured the Unified Shader architecture — an array of unified and similar compute hardware units in a GPU, in contrast to traditional graphics pipeline units with specialized functions such as rasterization and pixel shading [104] — adding momentum to the rise of generalpurpose computing on GPUs, often known as GPGPU. The success of GPUs was fuelled further by the introduction of CUDA (maintained by NVIDIA) and OpenCL (maintained by the Khronos Group) — the parallel computing platform and programming models that bolstered the general-purpose ecosystem around GPUs. CUDA and OpenCL enabled GPUs to be used pervasively by the high performance computing community across different domains by allowing users to conveniently express the parallelism in their applications using these programming platforms. As a result, the current generation of GPUs have not only pushed the gaming industry forward by leaps and bounds, but have also emerged as a cornerstone of high performance computing for a variety of general-purpose application domains.

In this chapter, we delve into the finer details of modern GPU computing and provide

Figure 2.1: CUDA program structure

the necessary background for the remainder of this thesis. Note that we restrict our discussion to NVIDIA GPUs as these are arguably the most prevalent discrete GPUs in the industry. However, as GPUs from other vendors feature similar architectural features, memory system organization and programming models, we expect our observations to be applicable to other GPU architectures as well. In the remainder of this chapter, we first present the CUDA programming model in Section 2.1, followed by an overview of a modern NVIDIA GPU architecture in Section 2.2.

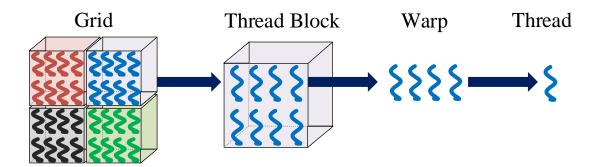

## 2.1 Programming Model

In a typical CPU-GPU system with a discrete GPU, the CPU is referred to as the *host* and executes the serial or modestly data parallel sections of the application, whereas the GPU is referred to as the *device* and executes the highly data parallel sections of the applications. CUDA — formerly an acronym for Compute Unified Device Architecture — is the standard parallel computing platform and programming model developed by NVIDIA for its GPUs [32]. Figure 2.1 depicts a typical program structure in CUDA. A CUDA program consists of data parallel structures called *kernels* that comprise tens of thousands of threads. The host CPU launches the kernel on the device GPU as a multidimensional *grid* of threads. Within a kernel, the large number of threads are organized into structured blocks of computation known as *thread blocks*. A device-level hardware scheduler in the GPU schedules the thread blocks to the different GPU cores for execution. The policy to schedule thread blocks on GPU cores can have a considerable impact on performance and has been evaluated in prior work [75, 96, 154, 155, 102].

The maximum number of thread blocks that can be co-scheduled on each GPU core at a given time is governed by the occupancy constraints specified by the vendor on

various system resources such as registers and threads. Therefore, the number of thread blocks available for multithreading is restricted by the demand for constrained resources posed by each thread block. Nevertheless, such a policy accords dynamism to GPUs in determining the number of thread blocks that can be scheduled concurrently on each GPU core, instead of restricting it to a constant number. As a result, it grants users the flexibility to examine the trade-off between a smaller number of thread blocks per GPU core, where each thread block is allotted higher resources, and a higher number of thread blocks per GPU core, where each thread block is allotted fewer resources. Expert programmers try to optimize their programs in order to maximize resource usage without significantly sacrificing the degree of multithreading available on each GPU core present in form of thread blocks [118, 83]. In addition, several mechanisms have been proposed to relieve the programmer from the burden of computing the best trade-off between the number of thread blocks and the resources allotted to each thread block [13, 134, 135, 152, 105, 14, 164, 159].

The different thread blocks in a kernel are executed independently and can be scheduled in any order. While threads within a thread block can be synchronized using a barrier synchronization primitive in CUDA called \_syncthreads(), threads across different threads blocks cannot be directly synchronized using similar programming primitives. However, different thread blocks can communicate and collaborate implicitly through the global memory. In addition, synchronization across thread blocks can generally be enforced through the CPU by terminating and relaunching the kernel at the desired synchronization points. However, such coarse CPU-driven thread block synchronization occurs at a significant cost of additional communication between the host and the device [147]. Several recent proposals have discussed methodologies to extend or improve the existing synchronization primitives in GPUs through schemes pertaining to GPU barrier synchronization [41, 160, 147, 114, 163, 168] and scope synchronization [122, 142, 6], among others.

Each thread block consists of several smaller group of threads called *warps* — the smallest granularity for scheduling threads within a GPU core. The threads within a warp execute in a Single-Instruction Multiple-Threads (SIMT) fashion where the hardware functional units execute the same instruction across multiple threads of a warp in lockstep before moving to the next instruction. Instructions executed by the hardware are called SIMD instructions, *i.e.*, Single-Instruction Multiple-Data. SIMD instructions operate on a vector of data, instead of scalar data items. The length of the vector is known as the SIMD width.

In the case of control flow instructions, such as conditional branches, threads within a warp may take different execution routes after resolving their branch condition. This phenomenon is referred to as warp divergence. In such a scenario, hardware executes the divergent sets of threads sequentially until they converge and continue lockstep execution. High levels of control flow divergence often sacrifices the benefits of parallelism, and this has been addressed extensively in prior work [45, 113, 133, 39]. In most CUDA-enabled GPU architectures, warp divergence also prevents the divergent group of threads from communicating and sharing data due to their sequential execution. The recent Volta architecture, however, supports independent thread scheduling by maintaining per-thread scheduling resources (such as the program counter), instead of per-warp scheduling resources. This gives finer thread scheduling control and allows divergent threads to execute instructions in an interleaved fashion, enabling fine-grained communication and synchronization between threads within a divergent warp [108]. Volta still follows the SIMT execution model as the same instruction is executed by all active threads in a warp at any point in time, albeit with more flexible interleaving between divergent threads.

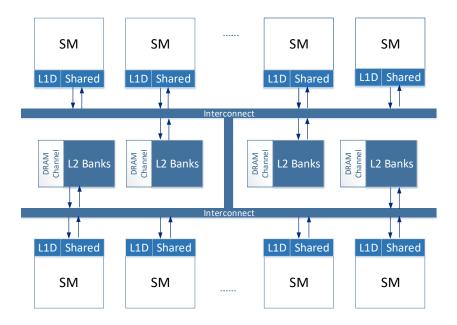

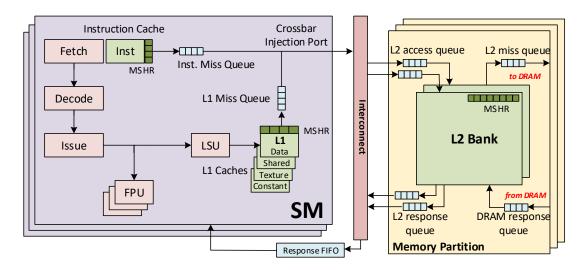

#### 2.2 GPU Architecture

A typical GPU consists of several functional units organized as a set of highly multithreaded and pipelined cores that are referred to as *Streaming Multiprocessors* or *SMs*. Figure 2.2 depicts a system-level diagram of a typical GPU. Each SM comprises a unified shader pipeline consisting of fetch, decode, issue, execution and write-back stages. The fetch stage retrieves the warp instructions from the instruction buffers, while the decode stage resolves the operands and their associated dependencies. The dependency between operands is recorded through a *scoreboarding* mechanism. The scoreboard tracks the read-after-write (RAW) and write-after-write (WAW) dependency hazards within and across warps by reserving registers for the decoded destinations that require updating. If a subsequent instruction reads or writes a reserved register, a dependency is flagged, which is then resolved at the write-back stage on completion of the pending memory operation. Figure 2.3 illustrates these stages diagrammatically in greater detail. More architectural details can be found in [141].

<sup>&</sup>lt;sup>1</sup>In this thesis, we use the terms "core" and "SM" interchangeably, when referring to GPUs.

Figure 2.2: System-level architecture of a typical GPU

#### 2.2.1 Warp Scheduling

Each SM consists of multiple hardware warp schedulers (not shown in the figures). After the decode stage, a warp scheduler selects a warp from a pool of active warps and issues them to the functional units, i.e., floating-point unit (FPU) or load-store unit (LSU). A warp is termed active only when there exists a warp instruction that has all the operands required for execution and the scoreboard detects no dependency hazard with any outstanding memory operation. Once an active warp instruction is issued, it is scheduled and executed in lockstep on the appropriate functional units, depending on the instruction type. These functional units comprise multiple lanes of compute (floatingpoint) and memory (load-store) pipelines. Furthermore, if the scoreboard detects a dependency hazard with a pending memory operation, the corresponding warps are descheduled and forced to stall. Such warps are referred to as *inactive warps*. The inactive warps do not participate in multithreading until the pending memory operations are completed. In such a scenario, the warp scheduler selects a warp from the pool of active warps to replace the stalled inactive warp and allows continued execution, thereby overlapping the latency of pending memory operations. When the pending memory operations are completed, the missing operands are made available, thereby triggering the write-back stage for pending memory instructions. As a result, the formerly reserved registers are released and dependency hazards at the scoreboard are resolved. However, in the event when no active warps are available, the functional units are forced to stall

Figure 2.3: Baseline GPU architecture

and multithreading no longer hides the latency of outstanding memory operations. As a result, memory latencies appear in the critical path and directly impact performance. Memory-intensive applications are more susceptible to such a scenario due to the high frequency of memory instructions that can potentially lead to a long latency memory operation.

#### 2.2.2 GPU Memory Hierarchy

Modern GPUs feature a memory hierarchy with impressively diverse memory units, catering to a wide spectrum of request types supported by GPUs. We now explore the different levels of the memory hierarchy and discuss some of their individual properties. More details can be found in [141, 32].

**Register Files.** In each SM, multi-banked register files occupy the highest level in the memory hierarchy to enable fast context switching between warps [113, 1, 111]. The register file is indexed by warp id and register id, and is used to store private data for thousands of concurrent threads under execution. Typical modern GPUs, such as Kepler, feature up to 65,536 32-bit registers per SM which amounts to 256 KB of register file per SM. This is in stark contrast to traditional multiprocessors which feature only a few hundred (or fewer) registers in the register file.

L1 Caches. The next level in the memory hierarchy is formed by the private caches within the SM. These caches (enumerated below) include read-write memories such as Shared Memory and L1 Data Cache, and read-only memories such as Constant Cache, Texture Cache and Instruction Cache.

- 1. Shared Memory: The shared memory is allocated explicitly by the programmer at thread block granularity and acts like a scratchpad for the programmer. The shared memory data is private to the thread block for which it is allocated. CUDA provides the \_shared\_ memory space specifier to declare and allocate shared memory in the device code. Shared memory is heavily banked to allow simultaneous access to data for all threads of a warp in a single cycle. However, poor memory access patterns can lead to bank conflicts, thereby serializing the accesses and slowing down the warps [50, 165, 68].

- 2. L1 Data Cache: The L1 data cache is primarily used for caching global memory accesses.<sup>2</sup> Global memory is declared in CUDA using the \_\_device\_\_ memory space specifier and can be accessed globally by all threads of a grid. The scope of global memory also extends to the host, and therefore host and device can transfer data in the global memory space. Furthermore, the L1 data caches are non-coherent and employ write-through, no-write-allocate policies for global memory accesses. This implies that a write in the global memory space is performed directly in the shared L2 cache, bypassing (on a write miss) or evicting (on a write hit) the L1 data cache. However, GPUs support a weak memory consistency model [40, 4], and therefore shared data in the remaining L1 data caches is not invalidated upon a write, potentially allowing other SMs to continue reading stale data from their respective L1 data caches. Therefore, to access the most recent data in the global memory space, the programmer or the compiler must explicitly bypass (and invalidate) the L1 data caches that can cache potentially stale data and must read directly from the L2 cache.

In addition to global memory accesses, the L1 data cache also supports local memory accesses. Local memory is private to each thread and is declared in CUDA using the \_local\_ memory space specifier. The L1 data cache employs a write-back, no-write-allocate policy for local memory accesses. Compilers use local memory space for a thread when there are not enough registers in the register file to store private thread data.

3. *Constant Cache*: The constant cache is used for caching constant memory accesses. The constant memory is declared in CUDA using the \_constant\_ memory space specifier. Constant memory is read-only memory and can be accessed by all threads of a grid. Similar to global memory space, the scope

<sup>&</sup>lt;sup>2</sup>In the remaining chapters, we refer to L1 data cache simply as L1 cache, unless otherwise specified.

for constant memory extends to the host, allowing host and device to transfer read-only data in the constant memory space. Constant memory is typically used when all threads of a warp read from the same memory location and the data is not expected to change over the course of execution.

- 4. *Texture Cache*: The texture cache is used for caching texture memory accesses. The texture memory is a read-only memory that provides a global scope and is assigned using device functions [32]. Typically, texture memory is used in scenarios when threads of a warp issue reads to contiguous memory addresses, exhibiting high spatial locality.

- 5. *Instruction Cache*: The instruction cache is a read-only cache accessed during the fetch stage by each warp. A warp that has a valid instruction in the instruction cache fills the instruction buffer and eventually proceeds to the decode stage. However, in case of a miss in the instruction cache, a memory request is generated and the corresponding warp is descheduled if there are no more instructions to be decoded in the instruction buffer for that warp.

**L2 Cache.** The private caches are backed by a shared L2 cache that adopts a write-back, write-allocate policy for L2 write requests. As shown in Figure 2.3, L2 cache is organized into multiple banks. A group of L2 banks form a *memory partition* sharing a common channel to the off-chip DRAM. The requests to the L2 cache enter the memory partition through the *L2 access queues*. Upon a read hit, the L2 cache line is read out through the data port in the L2 cache into the *L2 response queues*. On a read miss, a cache line is reserved in the L2 cache and a read to the DRAM is issued through the *L2 miss queue*. When a fill request is received from the DRAM through the *DRAM response queue*, the reserved cache line is filled and a subsequent fill request is generated for the L1 cache, if required.

Interconnection Network. Each L2 cache bank communicates with the cores through a *crossbar* interconnection network. There are separate interconnection networks for the request path (cores to L2 cache) and the response path (L2 cache to cores). The request path carries read requests and write requests, whereas the response path carries read responses and write acknowledgements. The crossbar transfers packets at the granularity of *flits*. In an uncongested memory system, L2 cache has an access latency of around 120 cycles from the L1 cache for non-texture accesses [141]. However, congestion and queueing delays due to bandwidth limitations can considerably increase the latency to access the L2 cache and DRAM. For instance, due to large cache

line size, it often takes around 4-5 cycles just to push a single cache line through the crossbar router at 32-byte flit granularity. As a result, for memory-intensive applications that present a high demand on the interconnect, the cumulative queueing delay to push multiple cache lines can be considerably high.

Graphics DRAM. The shared L2 cache is further backed by an off-chip graphics DRAM or GDDR that has an additional access latency of around 100 cycles, excluding the arbitration delays within the DRAM. Each memory partition has a memory channel with an independent DRAM command scheduler queue where the DRAM requests wait until the corresponding memory access commands are scheduled to the DRAM. DRAM scheduler employs a FR-FCFS (First-Row First-Come-First-Serve) scheduling policy to select a new request from the scheduler queue. Furthermore, each memory partition is associated with multiple DRAM chips, where each DRAM chip is organized into multiple banks. Multiple banks of a DRAM chip share a common bus that determines the peak memory bandwidth of the DRAM. Values for the above DRAM parameters used in this thesis are listed in Table 3.1 in the next chapter.

#### 2.2.3 Memory Coalescing

Bandwidth is a critical resource in throughput-oriented architectures such as GPUs. Therefore, GPUs employ several mechanisms to reduce the bandwidth demand on the memory hierarchy. One such important technique is known as *memory coalescing*. As threads in a warp operate on a vector of data, each thread can potentially generate an independent memory request. When such threads generate highly regular memory accesses, i.e., to consecutive words in the memory, all accesses span across a few cache lines only. In such a scenario, the load-store unit coalesces the memory requests that fall within the same cache line into a single request to the memory hierarchy. For instance, when a warp with 32 threads access 4-byte words starting from a 128-byte aligned address, all the addresses fall within a single cache line, assuming 128-byte cache line size. As a result, 32 threads of a warp generate a single, highly coalesced memory request. This phenomenon is known as memory coalescing. Such regular access patterns, combined with memory coalescing, improve memory bandwidth by allowing multiple loads to be serviced by fewer memory requests. In a different scenario, where threads access words at 128-byte offset, warp generates 32 different memory requests — one for each thread of the warp — significantly depleting memory bandwidth. Such access patterns are known to exhibit high memory divergence [33, 136, 60, 84]. Programmers

often try to optimize the memory access patterns to reduce memory divergence in order to maximize bandwidth [83].

After coalescing memory requests in the load-store unit, GPUs exploit another opportunity to reduce the bandwidth demand on the memory hierarchy. This is done through Miss Status Holding Registers (MSHRs) in the L1 and L2 caches. MSHRs are fully-associative arrays and are used to track outstanding memory requests. For every cache miss in progress, an MSHR entry is allocated in the corresponding cache. Subsequent accesses to the pending cache lines are merged into an existing MSHR entry that corresponds to the same address. Therefore, it eliminates redundant memory requests to the lower levels of the memory hierarchy for cache lines that are already being fetched. In other words, for every miss at the L1 and L2 caches, corresponding MSHR entries are searched for an outstanding request for the same cache line. If no existing entry is found, a new MSHR entry is created to track the new cache miss in progress. However, if an entry is found in the MSHRs, the new cache miss is merged with an existing MSHR entry that corresponds to the same cache line. Once the pending memory request is serviced, the associated MSHR entries are freed and warps associated with all the merged requests are serviced. Limiting the number of MSHR entries also limits the maximum number of memory requests that can be in-flight at any time in the memory system. Therefore, MSHRs determine the peak bandwidth demand that each level of the memory hierarchy can pose on the lower levels of the memory hierarchy.

## **Chapter 3**

# Evaluating and Mitigating Bandwidth Bottlenecks

In comparison to the traditional multiprocessors, GPUs present significantly different requirements to the memory system. This is largely because of the throughput-oriented nature of GPUs — a marked departure from the single-threaded and latency-oriented processors. In GPUs, a large number of requests are made to each level of the memory hierarchy in order to sustain the enormous parallelism in GPU cores. However, with increasing off-chip bandwidth with newer memory technologies (such as HBMs) on one side, and increasing number of streaming multiprocessors on the other side, the intermediate cache hierarchy appears to be under-provisioned to handle such high volumes of memory traffic. As a result, the bandwidth bottleneck — traditionally limited to the off-chip memory — is distributed across the entire memory hierarchy, including the cache hierarchy. This motivates us to further evaluate and understand the bandwidth bottlenecks in GPUs so that we can provision the memory hierarchy with adequate bandwidth resources and ensure a well-performing memory system.

#### 3.1 Overview

In this chapter, we aim to characterize the severity of the bandwidth problem posed by the three levels of the memory hierarchy, viz., private L1s, shared L2 and off-chip memory, and also characterize the role of their peripheral network elements such as interconnects and buffers. We show that due to bandwidth bottlenecks, there is severe congestion between the L1 and L2, as well as between the L2 and off-chip memory. As discussed in Chapter 1, such high levels of congestion lead to increased memory

Figure 3.1: Issue-stall cycles, Average Hit Latencies to L2 (L2-AHL) and Average Memory Latencies (AML) for memory-intensive applications.

latencies, which has three major implications. Firstly, in memory-intensive applications, due to insufficient computation to mask high memory latencies, such latencies appear in the critical path of system performance. Secondly, high latencies of outstanding miss requests lead to prolonged contention of cache resources such as Miss Status Holding Registers (MSHRs) and replaceable cache lines. This effect increases the memory latencies even further as succeeding requests get serialized and have to wait for outstanding misses to complete and relinquish the resources. And thirdly, back pressure from a congested lower level further throttles the cache pipeline and prevents it from operating at peak throughput, exacerbating the bandwidth limitation in the cache hierarchy. A combination of the above factors force the cores to stall, leading to performance degradation. In Figure 3.1 we show that a set of representative memoryintensive applications, run on a simulated GTX 480 GPU, exhibit high average memory latencies (AML; 452 cycles on average) and spend a considerable fraction of application run time in a stalled state (62% on average) waiting for memory operations to complete. Additionally, high average L2 hit latencies (L2-AHL; 303 cycles on average) indicate that there is considerable congestion between the private L1 and the shared L2 cache, and therefore suggests that the high average memory latencies are due to bandwidth limitations in both the cache hierarchy and to off-chip memory.

In order to reduce congestion in the memory system, we explore several design choices at each level of the memory hierarchy and evaluate their efficacy in alleviating the bandwidth bottleneck. We conduct a design space exploration and show that solving the problem in isolation, at specific levels of the memory hierarchy, can give suboptimal results and can even be counter-productive, only creating even more congestion

elsewhere in the memory system. For instance, we observe that to prevent throttling of the L1 cache, increasing the L1 bandwidth by increasing the number of MSHR entries to handle more outstanding misses can lead to performance degradation due to even higher congestion between L1 and L2. We verify this observation on a real GTX 480 GPU chip by increasing the core frequency, effectively increasing the L1 request rate, and observe a performance degradation (detailed discussion in Section 3.6). On the other hand, matching the increased bandwidth demand of L1 at the L2 cache significantly improves performance, and this even exceeds the performance achieved by a memory system with baseline cache hierarchy and High Bandwidth Memory (HBM) DRAM. Therefore, in order to efficiently solve the bandwidth bottleneck, we show that it is imperative to address the bandwidth demands of different memory levels in tandem and provide a synergistic solution. Additionally, we use the insights developed in this chapter to perform a cost-benefit analysis and propose efficient ways to mitigate the bandwidth bottlenecks at different levels of the memory hierarchy. Overall, this chapter expands the understanding of the bottlenecks across the GPU memory hierarchy and serves as a guide for architects and programmers to optimally scale bandwidth of the memory hierarchy and write bandwidth-sensitive programs, respectively.

Organization: The remainder of this chapter is organized as follows. Section 3.2 presents the evaluation methodology and infrastructure adopted in this chapter. Section 3.3 motivates the need for this study by showing that the bandwidth bottlenecks across the memory hierarchy in GPUs breach the latency tolerance property of GPUs by causing congestion. Section 3.4 quantifies the congestion levels across the GPU memory hierarchy and explores the architectural causes. Section 3.5 present the various design choices in the memory system to mitigate the bandwidth bottlenecks, derived from the characterization of congestion across the memory hierarchy. Section 3.6 evaluates the efficacy of mitigating the bandwidth bottlenecks through guided design space exploration. Section 3.7 identifies cost-effective configurations of the memory hierarchy and shows that synergistic scaling of L1 and L2 cache resources can reasonably match or even exceed the benefits of an HBM DRAM, leading to a performance improvement of up to 29% on average with a minimal area overhead of 1.5%. Section 3.8 discusses the relevant related work. Section 3.9 concludes the chapter by summarizing the findings and results.

Parameter Value Core 15 SMs, Greedy-then-oldest (GTO) scheduler Clock frequency Core @ 1.4 GHz; Crossbar/L2 @ 700 MHz Threads per SM 1536 Registers per SM 32768 48 KB Shared Memory L1 Data Cache 16KB, 128B line, 4-way, LRU, write-evict, 32 MSHR entries, 8-entry miss queue Interconnect Crossbar, Fly-topology, 32B flit size L2 Cache 768 KB, 128B line, 8-way, LRU, write-back, 12 banks, 32 MSHRs, 8-entry miss queue, 32B data port width, 8-entry request queue DRAM GDDR5 DRAM, Command clock 924 MHz, FR-FRCFS 384 bits net buswidth, 6 Memory Partitions, 2 DRAM chips/partition, 32-bits buswidth/chip, 8 bytes burst length, 16 DRAM banks/chip **DRAM Timing Constraints** CCD = 2, RRD=6, RCD=12, RAS=28, RP=12, RC=40, CL=12, WL=4, CDLR=5, WR=12

Table 3.1: Baseline architecture parameters for GPGPU-Sim

# 3.2 Background

In this section, we describe the evaluation framework used in the rest of the chapter. This includes the target architecture, simulation framework and target workloads.

#### 3.2.1 Baseline Architecture

In this study, we consider a baseline GPU architecture similar to NVIDIA's Fermi architecture [115, 141]. Notably, as the organization of the memory hierarchy is fairly consistent across different architectures, we expect our observations to be applicable to Kepler and Maxwell as well.

#### 3.2.2 Simulation Framework

We model a GTX 480 Fermi GPU on a cycle-accurate simulator GPGPU-Sim (v3.2.2) [10] with the baseline architectural parameters listed in Table 3.1. We use GPUWattch [98] to compute the area and power in our experiments. GPGPU-Sim shows a high performance correlation of over 97% against a Fermi GPU [141] and has been widely used in prior works [132, 1, 121, 139, 5], and therefore reliably represents our findings.

Table 3.2: List of workloads.  $P_{\infty}$ : Speedup with infinite bandwidth memory system;  $P_{DRAM}$ : Speedup with a baseline cache hierarchy and infinite bandwidth DRAM.

| #  | Suite     | Benchmark                   | Benchmark Abbreviation $P_{\infty}$ |      | P <sub>DRAM</sub> |

|----|-----------|-----------------------------|-------------------------------------|------|-------------------|

| 1  | MapReduce | Matrix Multiplication       | x Multiplication mm                 |      | 1.01              |

| 2  | Parboil   | Lattice-Boltzman Method     | lbm                                 | 3.40 | 1.87              |

| 3  | MapReduce | Similarity Score            | SS                                  | 3.23 | 1.00              |

| 4  | Rodinia   | Nearest Neighbour           | nn                                  | 3.11 | 1.84              |

| 5  | Rodinia   | Hybrid Sort                 | hybridsort                          | 3.10 | 1.24              |

| 6  | Rodinia   | Computational Fluid         | cfd                                 | 3.08 | 1.06              |

| 7  | MapReduce | Page View Rank              | pvr                                 | 2.89 | 1.01              |

| 8  | Rodinia   | Breadth-First Search        | bfs                                 | 2.84 | 1.00              |